# Sixth Semester B.E. Degree Examination, June/July 2024 **VLSI Design and Testing**

Time: 3 hrs.

C.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

## Module-1

State Moore's law, elaborate with graph. 1

(04 Marks)

Derive the expression for drain current in linear and saturation regions. b.

(10 Marks)

- Explain the following non-ideal characteristics:

- i) Body effect

- ii) Channel length modulation.

(06 Marks)

#### OR

- Explain working of nMOS enhancement mode transistor operation with neat sketches and 2 relevant equations. (08 Marks)

- Draw inverter circuit and explain its DC transfer characteristics. b.

(08 Marks)

Draw the schematic of

i)

$$F = A + BC$$

ii)

$$F = AB + CD$$

.

(04 Marks)

#### Module-2

Explain CMOS fabrication process with necessary diagrams. 3

(10 Marks)

With relevant equations explain transient response of CMOS inverter. b. With neat diagrams explain layout design rules.

(05 Marks) (05 Marks)

#### OR

Draw the stick diagram and layout of three input NAND gate. a.

(06 Marks)

Find maximum and minimum rise time and fall time delays of two input NAND gate. b.

(06 Marks)

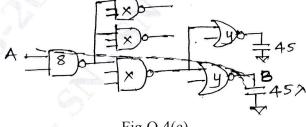

Estimate the minimum delay of the path from A to B in Fig.Q.4(c) and choose transistor sizes to achieve this delay. The initial NAND2 gate may present a load of 8λ of transistor width on the input and the output load is equivalent to  $45\lambda$  of transistor width.

Fig.Q.4(c)

(08 Marks)

### Module-3

Explain the operation of three transistor DRAM cell with necessary timing diagrams. 5

(08 Marks) (06 Marks)

- Draw the structure of NAND flash memory cell and explain the operation. b.

- Explain ferroelectric RAM with necessary diagrams.

(06 Marks)

#### OR

- Explain read and write operations of SRAM cell with necessary diagrams. (08 Marks) 6 (06 Marks) What is row decoder? Explain with an example. b. (06 Marks)

- Explain data programming and erasing methods of flash memory. C.

## Module-4

Briefly explain different types of faults in digital circuits. (08 Marks) 7

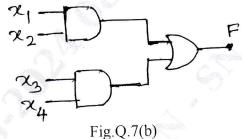

Consider the logic circuit shown in Fig.Q.7(b) find Boolean difference with respect to  $x_3$ .

(06 Marks)

(10 Marks)

Explain detection of multiple faults in combinational logic circuits. (06 Marks)

### OR

With neat sketch, explain path oriented decision making algorithm. (10 Marks) 8 For a given logic network determine tests for checking all single node faults (Fig.Q.8(b))

$F = \bar{x}_1 x_2 \bar{x}_3 + \bar{x}_1 \bar{x}_2 \bar{x}_3$ Fig.Q.8(b)

## Module-5

Briefly explain: (06 Marks) ii) Observability. i) Controllability Explain adhoc design rules for improving testability. (06 Marks) (08 Marks) With neat diagram explain partial scan.

OR

10

(10 Marks) List LSSD design rules. (10 Marks) Explain test generation based on functional fault models.