# Third Semester B.E. Degree Examination, Dec.2024/Jan.2025 **Analog Electronic Circuits**

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

# Module-1

- Write a Diode circuit which clips the voltage above +7V and below +4V. Explain its 1 operation with input voltage of 15 sinwt. Write input and output voltage waveform and also transfer characteristics. Assume Ideal Diode.

- Analyze collector-to-base Bias circuit to obtain expressions for I<sub>B</sub>, I<sub>c</sub> and V<sub>CE</sub> and there by derive an expression for  $S_{ICO}$ .

- c. A voltage divider Bias circuit has upper Resistor  $R_1 = 18 \text{ k}\Omega$ , lower Resistor  $R_2 = 2 \text{ k}\Omega$ ,  $R_C = 10 \text{ k}\Omega$ ,  $R_E = 1 \text{ k}\Omega$ ,  $V_{CC} = 20 \text{ V}$ , and  $\beta = 100$ . Using exact analysis, find  $V_C$ ,  $V_{CE}$ ,  $I_C$  and V<sub>CB</sub>. Indicate the operating region.

### OR

- Write the circuit which clamps Negative peak of 16V peak-to-peak square wave to -2V. 2 Explain its operation with input and output waveforms. Assume Ideal Diode. (06 Marks)

- Design Emitter stabilized bias circuit using  $V_{CC} = 20V$ ,  $V_{CEO} = \frac{1}{2} V_{CC}$ ,  $I_{CO} = 3mA$ ,  $\beta = 100$ ,  $R_C = 5R_E$ . Write the circuit. (07 Marks)

- Write transistor switching circuit and explain the switching characteristics of transistor with (07 Marks) graph.

- Using h-parameter equation, define h-parameter for a 2-port network and write h-model. 3 (06 Marks)

- State and prove Miller's Theorem. b.

(06 Marks)

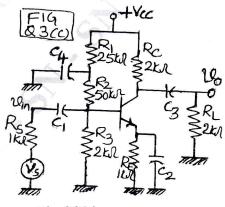

Transistor used in amplifier circuit show in Fig Q3(c), has  $h_{ie} = 1.1 \text{ k}\Omega$ ,  $h_{fe} = 50$ ,  $h_{ce} = 0$ ,  $h_{re} = 0$ . Find  $A_I$ ,  $Z_{in}$ ,  $Z_0$   $A_V = \frac{V_0}{V_c}$  &  $A_{VS} = \frac{V_0}{V_c}$ .

Fig Q3(c)

(08 Marks)

OR

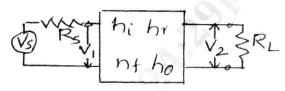

4 a. For the 2-port network shown in Fig Q4(a), derive an expression for  $A_I$ ,  $Z_{in}$   $A_V$  and  $Z_0$  interms of h-parameters,  $R_S$  and  $R_L$ .

Fig Q4(a) (06 Marks)

Using simplified (approx) h-model of CE configuration, analyze common base amplifier to derive an expression for  $A_I$ ,  $Z_{in}$ ,  $A_V$  and  $Z_0$ .

c. Transistor used in RC coupled CE amplifier with fixed Bias has  $h_{ie}=1~k\Omega,~h_{fe}=60,~h_{oe}=15~\mu\text{A/V},~h_{re}=2*10^4.$  Calculate has  $R_S=1~k\Omega,~R_B=56~k\Omega,~R_C=10~k\Omega$  and  $R_L=10~k\Omega.$  Find  $A_I,~A_{IS}~Z_{in}$  and  $Z_0.$

Module-3

5 a. Explain why cascading is required. Write Block diagram of 4-stage cascaded amplifier and derive an expression for overall gain of the system in-terms of individual gains. (06 Marks)

b. With the help of circuit diagram and waveforms explain Darlington Emitter follower.

Mention two important features of this circuit.

(06 Marks)

c. With the help of block diagram, briefly explain Negative Feed Back System. What are the advantages of Negative Feed Back in Amplifier? (08 Marks)

OR

6 a. Derive an expression for output impedance in voltage shunt Feed Back and Input Impedance in voltage series Feed Back amplifiers. (08 Marks)

b. An amplifier with Negative Feed Back has closed loop gain of 20. An input of 50 mV is required to produce certain output without Feedback, write 0.5V input is required to produce same output with Negative Feedback. Find open loop gain and Feed Back factor. (05 Marks)

c. Two amplifiers are cascaded with  $R_L = 20 \text{ k}\Omega$ ,  $R_S = 2 \text{ k}\Omega$ Stage 1 : No load Gain = 1, Input Impedance =  $500 \text{ k}\Omega$ , Output Impedance =  $1 \text{ k}\Omega$

Stage 2: No-load gain = 300, Input Impedance =  $1 \text{ k}\Omega$ , output Impedance =  $50 \text{ k}\Omega$

Find i) loaded gain of each stage ii) current gain of cascaded system iii) total overall voltage gain of cascaded system with  $R_S(V_L/V_S)$ . (07 Marks)

Module-4

7 a. With a circuit, Graph/waveform, explain the operation of class 'B' push pull amplifier.

Show that maximum conversion efficiency is 78.5%. (08 Marks)

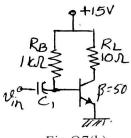

b. A series fed class A power amplifier shown in Fig Q7(b) has input voltage generating ac base current of 12mA (Max). Find input power, output power, efficiency and power dissipated.

Fig Q7(b)

(05 Marks)

c. Write the circuit of Wien Bridge oscillator and derive an expression for output frequency.

(07 Marks)

### OR

- 8 a. State Barkahusen criterion for sustained oscillations. Explain with circuit, how Barkhausen criterion is met in RC-phase shift oscillator. (08 Marks)

- b. Class B complementary power amplifier has a supply of  $\pm 15V$  and load of  $R_L=10\Omega$ . Find :

- i) Maximum ac power developed and the efficiency under maximum ac power condition

- ii) Maximum power dissipated per transistor and the efficiency under Max. Power dissipation condition. (06 Marks)

- c. Briefly explain electrical equivalent of a crystal. A crystal has L=1 H, C=0.01 pF,  $C_m=1$  pF, R=2 k $\Omega$ . Find series and parallel Resonant frequency and Q-factor. (06 Marks)

## Module-5

- 9 a. With circuit and small signal model of common source JFET amplifier using Fixed bias, derive an expression for  $Z_{in}$ ,  $Z_0$  and  $A_V$ . (06 Marks)

- b. Explain the construction, working and characteristics of n-channel depletion type MOSFET.

(08 Marks)

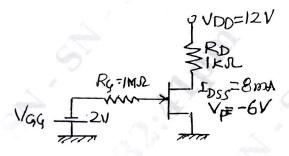

- For circuit shown in Fig Q9(c), find V<sub>GS(Q)</sub>, V<sub>DSQ</sub> V<sub>S</sub>, V<sub>G</sub>, I<sub>DQ</sub> and V<sub>D</sub>.

Fig Q9(c)

(06 Marks)

### OR

10 a. Compare JFET over MOSFET and BJT over MOSFET.

(06 Marks)

- b. Explain the construction, working and characteristics of n-channel JFET with neat sketch and graph.

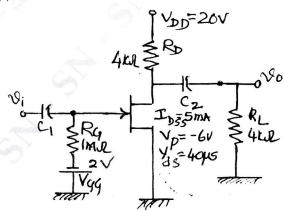

- c. For the circuit, shown in Fig Q10(c), find  $g_m$ ,  $r_d$ ,  $z_{in}$ ,  $z_0$ ,  $A_v$ . Write small signal model. Take  $V_{GS(O)} = V_{GG} = -2V$

Fig Q10(c)

(07 Marks)

\* \* \* \*

3 of 3