## CBCS SCHEME

| USN [ |  |  |  |  |  |  |  |  |  |  |  | 18EE46 |

|-------|--|--|--|--|--|--|--|--|--|--|--|--------|

|-------|--|--|--|--|--|--|--|--|--|--|--|--------|

# Fourth Semester B.E. Degree Examination, Jan./Feb. 2023 Operational Amplifiers and Linear ICs

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

## Module-1

1 a. Explain the general stages of op-amp with a neat block diagram.

(08 Marks)

- b. Define explain the following terms:

- i) Input Bias current

- ii) Input offset current.

iii)CMRR.

(06 Marks)

c. Explain with a neat circuit, scaling and averaging amplifier using op-amp in inverting configuration. (06 Marks)

#### OR

2 a. Explain with a neat circuit diagram, instrumentation amplifier.

(08 Marks)

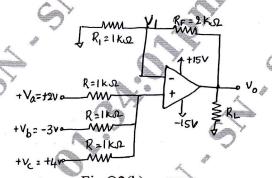

b. For the circuit shown in Fig.Q2(b), determine the voltage  $V_1$  at the non-inverting terminal and the output voltage  $V_0$ . Assume that the op-amp is initially nulled.

Fig.Q2(b)

(06 Marks)

C. What are the characteristics of an ideal op-amp? Also explain voltage transfer characteristics curve of an op-amp. (06 Marks)

### Module-2

- a. With a neat circuit diagram, explain working of an second order low pass filter and draw its typical frequency response curve. (10 Marks)

- b. Explain working and design of voltages follower regulator.

(06 Marks)

- c. Explain the following terms with respect to voltage regulator.

- i) Line regulation

- ii) Load regulation.

(04 Marks)

#### OR

- 4 a. Sketch the circuit of a series regulator that uses an IC op-amp as an error amplifier. Explain the circuit operation. Write equation for  $V_0$  terms of  $V_Z$ . (10 Marks)

- b. A DC power supply drops from 15V to 14.95V when the AC supply voltage falls by 10%. The output also falls from 15 to 14.9V. When the load current increases from zero to maximum. Calculate the source effect, load effect, line regulation and load regulation.

Module-3 Draw the circuit diagram of a triangular/rectangular waveform generator using op-amps. 5 Sketch the circuit waveforms, and explain its circuit operation. (10 Marks) b. Draw the circuit diagram of an op-amp RC phase shift Oscillator. Sketch the circuit waveforms, and briefly explain the oscillator operation. (10 Marks) OR Using a 741 op-amp, calculate resistor values for the inverting Schmitt trigger circuit to give 6 (04 Marks) triggering points of ±2V. With a neat diagram, explain: i) Comparator as zero crossing detector (08 Marks) ii) Voltage to current converter with grounded load.

Module-4

With a neat diagram, explain the non-inverting Schmitt trigger circuit.

With a neat circuit diagram, explain the operation of precision full wave rectifier as a 7 combination of half wave rectifier and a summing circuit. Also sketch the waveforms.

(08 Marks)

(08 Marks)

b. Explain the working principle of linear Ramp analog to digital converter. (06 Marks)

c. Design a non-saturating precision half-wave rectifier to produce a 2V peak output from a 1MHz sine wave input with a 0.5V peak value. Use a Bipolar op-amp with a supply voltage (06 Marks) of ±15V.

(10 Marks) Explain R – 2R ladder digital to analog converter circuit. 8

A linear ramp ADC uses a 10-bit counter and a 15KHz clock frequency. The counter output is to be 1111111111 when the input voltage is 100mV. Calculate the required ramp rate of (04 Marks) change and the ADC conversion.

Explain working ADC using successive approximation method.

(06 Marks)

Module-5

Draw the basic block diagram and waveforms for a PLL system. Identify each component (10 Marks) part and explain its function.

With a neat diagram, explain the internal architecture of IC 555 timer.

(10 Marks)

Explain how XOR Gates can be used as phase detector in PLL. (08 Marks) 10 Explain Monostable Multivibrator, realized using IC 555 timer. (08 Marks)

Define the terms related to PLL.

i) Tracking range

ii) Capture range.

(04 Marks)